Реферат: О возможности универсального кода внутреннего представления программы

Реферат: О возможности универсального кода внутреннего представления программы

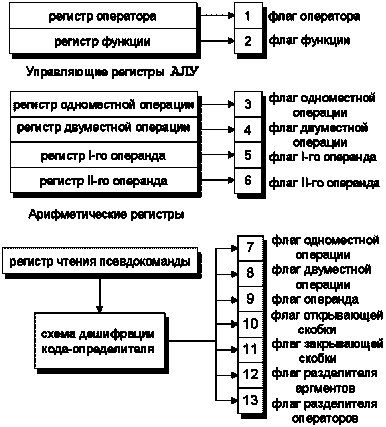

Сущность формульного процессора составляет зависимость выполнения команд от состояния загрузки регистров местной памяти. Для этого в качестве дополнительного звена в обычное подсоединение регистра чтения команды к устройству управления включается особый (главный) регистр автомата управления (РАУ; рис.2, 4), который также можно охарактеризовать как регистр формирователь-дешифратор кода команды управления. В роли этой команды выступает код, формируемый в РАУ в соответствии с состоянием загрузки регистров местной памяти и кодом очередной псевдокоманды (рис.4). Соответствие содержимого РАУ состоянию загрузки регистров местной памяти позволяет отслеживать текущее состояние вычислительного процесса и организовывать отработку очередного символа программы (т.е. очередной псевдокоманды) не только в зависимости от нее самой, но и от предшествующей части программы, выполнение которой создало данное состояние. Возможность соответствующего (однопросмотрового) алгоритма можно усмотреть, в частности, из общего «скобочного» принципа организации формульного вычисления: первой закрывается скобка (любого типа), которая была открыта последней. Иными словами, достаточно единственного (и даже общего) стека для адекватной организации сохранения промежуточных результатов. Подобным образом, оказывается достаточным малого числа информационных признаков (которыми выступают флаги загрузки регистров) для приведения зависимости вычисляющего алгоритма от общей структуры формулы к зависимости его фаз от этих признаков.

В отличие от обычного набора универсальных регистров арифметические регистры формульного процессора в силу их соответствия флагам загрузки несколько более специализированы. Хотя их основным назначением по-прежнему является временное сохранение кодов операций и операндов, каждый из них ориентирован на сохранение своего вида элементов формульного кода, которым может быть код оператора, функции, одноместной или двуместной арифметико-логической операции или их операнды (рис.4).

Таблица 3

Допустимые сочетания флагов загрузки арифметических регистров и их преобразования

| Флаги загрузки регистров (1, 2, 3, 4, 5, 6) | Установленный флаг в РАУ (7...13) 1 | Результирующий код после выполнения всех операций (1, 2, 3, 4, 5, 6 биты РАУ) |

| 0 0 0 0 0 0 | – | 1 0 0 0 0 0 |

| 1 (0) 0 0 0 0 |

7 |

1 0 1 0 0 0 |

| 1 (0) 0 0 1 0 |

8 |

1 0 0 1 1 0 |

| 1 (0) 1 0 0 0 |

9 |

1 0 1 0 1 0 |

| 1 (0) 0 1 1 0 |

7 |

1 0 1 1 1 0 |

| 1 (0) 1 0 1 0 |

8 |

1 0 0 1 1 0 |

| 1 (0) 1 1 1 0 |

9 |

1 0 1 1 1 1 |

| 1 (0) 0 1 1 1 |

8 |

1 0 0 1 1 0 |

| 1 (0) 1 1 1 1 |

8 |

1 0 0 1 1 0 |

В начальной фазе отработки очередного оператора РАУ находится в нулевом состоянии, а счетчик команд указывает на код текущей псевдокоманды, которая, при правильности формальной структуры программы, должна содержать код оператора. Выполнение этой «нулевой» (табл.3, первая строка) команды процессора состоит в переписывании кода оператора в регистр оператора, в силу чего соответственно переустанавливается флаг состояния его загрузки. Выборка последующей псевдокоманды завершает формирование новой команды управления. При загруженном регистре оператора процессор находится в режиме создания списка аргументов этого оператора. Этот режим завершается отработкой псевдокоманды, содержащей код разделителя операторов (флаг 13 на рис.4). К конечной фазе этой отработки в стеке (либо особо выделенных регистрах местной памяти) должны сформироваться адресно-литеральные псевдокоманды, представляющие вычисленные значения аргументов оператора, после чего инициируется выполнение данного оператора. При создании списка аргументов оператора процессор реализует вычисление соответствующих формульных выражений. Эти действия вытекают из логики обычного вычисления формулы и составляют наибольшее функциональное отличие формульного процессора от командного.

Рис. 4. Соответствие битов регистра автомата управления (РАУ) флагам загрузки регистров местной (внутрипроцессорной) памяти, предназначенных для сохранения и сборки кодов и операндов очередной выполняемой арифметико-логической операции

Базовый состав системы команд формульного процессора, включая управляющие команды, коды арифметико-логических операций и коды режимов адресации вполне укладывается в привычную сотню кодов. Добавляемые команды управления сопоставимы по сложности с командами перехода по счетчику или прерывания на подпрограмму. Принципиально, имеется три схемы выполнения команд управления. 1 – сохранение кода очередного элемента программы в подходящем регистре местной памяти; 2 – сохранение содержимого регистров местной памяти в стеке, подобное сохранению управляющих регистров при выполнении команды прерывания; 3 – наиболее сложные команды включают сопоставление приоритетов арифметико-логических операций, соответствующих прочитанному элементу программы и сохраненному в местной памяти либо в стеке. В зависимости от результата, в одном случае дальнейшее выполнение команды состоит в сохранении кода и операндов откладываемой операции в местной памяти и/или стеке (т.е. развивается по схеме 1 или 2), в другом – включается процесс выполнения накопленных отложенных операций и соответствующего освобождения ячеек стека и регистров местной памяти.

Таким образом, в результате, код арифметической или логической операции и ее операнды в формульном процессоре собираются при выполнении программы в арифметических регистрах из нескольких отдельных псевдокоманд и, возможно, результата выполнения предыдущей части программы, причем частью кода операции можно считать и код-определитель операнда, обеспечивающий извлечение из оперативной памяти в процессор данного, над которым производится действие. Выполнение арифметико-логических операций инициируется сигналами, вырабатываемыми при выполнении команд управления, а коды и операнды в момент инициирования находятся в соответствующих регистрах местной памяти.

Заключение

Формульный процессор, на наш взгляд, представляет собой систему с наиболее адекватным распределением функций между исполняющей схемой и программными системами низкого уровня (трансляторы, операционные системы и т.п.). Сохраняя уровень сложности и быстродействия, соответствующие обычным распространенным командным процессорам, формульный процессор позволяет не только разгрузить и упростить низкоуровневое программирование, но и значительно повысить общую прозрачность вычислительного процесса и контролируемость выполняемой программы. Дополнительным аргументом в пользу формульного подхода может служить характеристика соответствующего операторно-формульного кода как наиболее естественной и универсальной формы представления математических объектов алгоритмической природы, что создает основание и возможность для разработки соответствующих операторных кодовых стандартов, подобных таблице символов ASCII.

Список литературы

AndersonJ.P. A Computer for Direct Execution of Algorithmic Languages // Proc. EICC AFIPS, 20: Computers – Key to Total Systems Control. 1961. P.184.

Вычислительные машины с развитыми системами интерпретации. Под ред. В.М.Глушкова. Киев: Наукова Думка, 1970, 259с.

БулавенкоО.Н., ЯкубаА.А. Особенности архитектуры ЭВМ, реализующей языки высокого уровня и проектирование систем их интерпретации. Киев: Знание, 1986, 16с.

ОрганикЭ. Организация системы ИНТЕЛ 432. М.: Мир, 1987, 446с.

DijkstraE.W. // Communication ACM, 1968. V.11. №3, p.147.

КотовВ.Е., СабельфельдВ.К. Теория схем программ. М.: Наука, 1991, 248c.

Ляпунов А.А.В сб.: Проблемы кибернетики. Вып.1. М.: Физматгиз, 1958, с. 5.

ЯновЮ.И. В сб.: Проблемы кибернетики. Вып.1. М.: Физматгиз, 1958, с. 75.

КриницкийН.А., МироновГ.А., ФроловГ.Д. Программирование и алгоритмические языки. М.: Наука, 1975, 496с.

КонП. Универсальная алгебра. М.: Мир, 1968, 351c.

КозловМ.К. Формульный процессор с командоподобными логическими управляющими элементами. Патент РФ на изобретение №2143726 // Опубликован 27.12.99 Бюл. №36. См. также публикацию ВОИС WO 9904333 от 28.01.1999г.