Реферат: Подсистема памяти современных компьютеров

Реферат: Подсистема памяти современных компьютеров

Установка более одного банка памяти дает потенциальную возможность повышения производительности памяти за счет организации чередования банков (bank interleaving). Идею чередования проще пояснить на примере двух банков. Адресация памяти организуется так, чтобы ячейки, передаваемые в соседних тактах пакетного цикла, располагались в разных банках (сделать это несложно, поскольку пакеты выравниваются по границам строк кэша, которые фиксированы). Теперь контроллер памяти при передаче пакета будет обращаться к банкам поочередно, в результате чего частота передачи данных в такой системе может быть удвоенной по отношению к максимальной частоте работы отдельного банка. В чередовании может участвовать и большее число банков. Из разбиения на мелкие банки можно извлечь и другую выгоду. Поскольку современные процессоры способны параллельно выставлять несколько запросов на транзакции с памятью, скрытые фазы обработки запросов, обусловленные необходимым временем доступа, относящихся к разным банкам, могут выполняться одновременно. Однако это требует некоторого усложнения контроллера памяти и обеспечения независимости банков (возможности активации одного банка до предзаряда предыдущего). Независимость банков для асинхронной памяти достигается сугубо экстенсивным способом — увеличением числа линий интерфейса. Микросхемы SDRAM могут иметь внутреннюю 4-банковую организацию, независимость банков поддерживается синхронным интерфейсом. Чем больше будет независимых банков в ОЗУ, тем больше вероятность возможности их одновременного использования при обслуживании произвольных конкурирующих запросов.

|

Итак, подведем итоги развития, считая отправной точкой память FPM. Для повышения производительности:

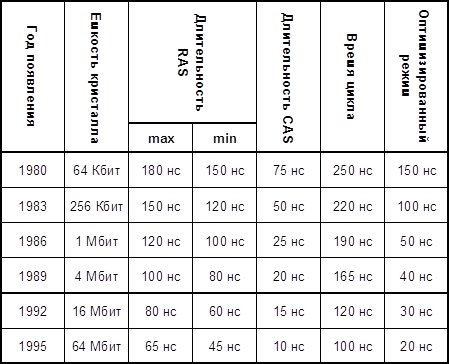

1. Повышают быстродействие ядра (запоминающих ячеек) — пока остановились на 40 нс.

2. Применяют конвейеризацию (внешнюю — память EDO, внутреннюю — BEDO и SDRAM).

3. Увеличивают количество независимых банков (в SDRAM — внутренне до четырех).

4. Увеличивают разрядность данных, для процессоров P5–P6 до 8 байт.

5. Повышают скорость передачи данных по интерфейсу памяти — в SDRAM частота “схода с конвейера” до 100–133 МГц, в DDR SDRAM — 2 х 100=200 МГц.

Пункты 3 и 4 сильно мешают прогрессу по п. 5 — 96 цепей к одному модулю развести без “перекосов” довольно сложно. Широкая разрядность интерфейса сковывает и масштабируемость памяти: нельзя увеличить объем ОЗУ, добавляя по одной микросхеме — можно только по четыре (а чаще по восемь).

Память Rambus DRAM

Память RDRAM (Rambus DRAM) имеет интерфейс, существенным образом отличающийся от традиционного и синхронного интерфейса. Запоминающее ядро этой памяти построено все на тех же КМОП-ячейках динамической памяти, но пути повышения производительности интерфейса совершенно иные. Первые микросхемы RDRAM применялись в некоторых моделях видеокарт и игровых приставок. Дальнейшим развитием интерфейса стал фирменный (Rambus) стандарт DRDRAM (Direct Rambus DRAM), обеспечивающий производительность 1600 Мбайт/с на двухбайтной шине данных при частоте 400 МГц. Стандарт DRDRAM поддержан множеством производителей микросхем и модулей памяти, он претендует на роль основного высокопроизводительного стандарта для памяти компьютеров любого размера. Подсистема памяти (ОЗУ) DRDRAM состоит из контроллера памяти, канала и собственно микросхем памяти. По сравнению с DDR SDRAM при той же производительности DRDRAM имеет более компактный интерфейс и гибкую масштабируемость. Разрядность ОЗУ DRDRAM (16 байт) не зависит от числа установленных микросхем, а число банков, доступных контроллеру, и объем памяти суммируется по всем микросхемам канала. При этом в канале могут присутствовать микросхемы разной емкости в любых сочетаниях.

Запоминающее ядро микросхем имеет многобанковую организацию — 64-мбитные микросхемы имеют 8 банков, 256-мбитные — 32 банка. Каждый банк имеет свои усилители считывания, благодаря чему в микросхеме может быть активировано несколько банков. Разрядность ядра 16 байт — 128 или 144 (с контрольными разрядами) бит. Ядро работает на 1/8 частоты канала, взаимодействие с ядром осуществляется по внутренним сигналам RAS и CAS. В современных DRDRAM применяются ячейки памяти с временем доступа 40–53 нс.

Память Direct RDRAM

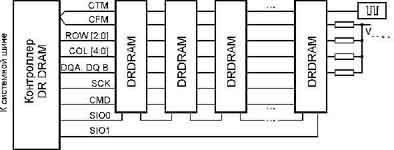

Канал DRDRAM (Rambus Channel) представляет собой синхронную последовательно-параллельную шину. Такой подход позволил ограничить количество линий интерфейса, что позволяет упорядочить разводку проводников ради повышения частоты передачи сигналов. Небольшое количество сигналов позволяет при разумной цене применить сверхбыстродействующие интерфейсные схемы. Тактовая частота канала — 400 МГц, стробирование информации осуществляется по обоим фронтам синхросигнала. Таким образом, пропускная способность одной линии составляет 800 Мбит/с. Канал состоит из 30 основных линий с интерфейсом RSL (Rambus System Logic) и 4 вспомогательных линий КМОП, используемых для инициализации микросхем. Стандарт требует соблюдения топологических правил, структура подсистемы памяти приведена на рисунке. Все основные интерфейсные линии, кроме линий синхронизации, начинаются от интерфейсной микросхемы контроллера памяти и заканчиваются терминаторами на противоположном конце канала. Терминаторы не позволяют сигналам отражаться от конца канала. Микросхемы памяти подключаются к каналу без T-образных ответвлений проводников, что облегчается их упаковкой в корпуса BGA (Ball Grid Array — матрица шариковых выводов). Интерфейсные линии должны идти строго параллельно друг другу с тем, чтобы задержки распространения сигналов по разным линиям совпадали. В канале может быть установлено до 32 микросхем, и все они соединены параллельно. Для того, чтобы контроллер мог адресоваться к определенной микросхеме, каждой из них назначается свой уникальный адрес DEVID. Нумерация микросхем (Device Enumeration) осуществляется в процессе инициализации, который выполняется с использованием вспомогательного последовательного КМОП-интерфейса.

Синхросигнал вводится в канал с дальнего конца и распространяется в сторону контроллера по линии CTM (Clock To Master). По этому сигналу микросхемы памяти стробируют данные, посылаемые к контроллеру (при чтении). Распространяясь по каналу, эти данные будут сохранять свою привязку к синхроимпульсам до самого контроллера. Дойдя до контроллера, синхросигнал выходит на линию CFM (Clock From Master) и идет по каналу до терминатора, установленного на конце.

По этой линии синхронизируется информация, посылаемая от контроллера к микросхемам памяти, и ее привязка к синхросигналу так же будет сохраняться в любом месте канала. Для самой дальней микросхемы время прохождения сигнала синхронизации от CTM до CFM не должно превышать 5 тактов (12,5 нс). Микросхемы привязывают данные чтения к синхросигналу с помощью встроенных схем DLL (Delay Locked Loop) для автоподстройки задержки сигнала DQS относительно CLK. Для повышения точности сигнал синхронизации передается в дифференциальной форме.

Физический уровень интерфейса учитывает волновой характер процессов распространения сигналов в канале. Передатчики микросхем памяти формируют сигналы с половинной амплитудой. Эти сигналы распространяются по шине в обе стороны, и на конце терминатора полностью поглощаются (отражения нет). На конце контроллера импеданс приемников высокий (терминаторов нет), и амплитуда сигнала из-за отражения удваивается. Таким образом приемник контроллера принимает сигнал полной амплитуды. Отраженный от контроллера сигнал дойдет до терминатора и поглотится им. По пути он никому не помешает, поскольку сигнал, передаваемый микросхемой памяти, “интересен” только контроллеру. Контроллер генерирует сигналы полной амплитуды, и по пути к терминаторам они в таком виде пройдут по всем микросхемам памяти.

Канал разделен на три независимые шины: 3-битная шина строк ROW[2:0], 5-битная шина колонок COL[4:0] и двухбайтная (2 х 9 бит) шина данных DQA[8:0] и DQB[8:0]. Дополнительный бит байта данных (имеется не у всех микросхем DRDRAM) может использоваться для контроля достоверности. По каждой шине информация передается пакетами, занимающими 4 такта (8 интервалов) синхронизации (10 нс). Пакет содержит 8 элементов, пакет строк имеет емкость 24 бит, колонок — 40 бит и данных — 16 байт по 8 или 9 бит.

По линиям ROW передаются пакеты для подачи команды активации (вызывает начало формирования внутреннего сигнала RAS), предзаряда (возврат его в исходное состояние), регенерации, управления энергопотреблением и термокалибровкой. По линиям COL могут передаваться пакеты команд чтения, записи и дополнительных команд, а также масок записи (может предотвращаться запись любых из 16 байт данных). По шине данных передаются пакеты данных для записи и чтения от памяти.

Высокая производительность шины управления (строк и колонок) позволяет отказаться от пакетных (в терминологии BEDO и SDRAM) передач и упростить протокол шины. Память может одновременно обслуживать до четырех транзакций на полной скорости передачи данных.

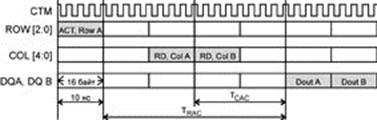

Транзакции чтения приведены на рисунке, по виду они аналогичны транзакциям SDRAM с тем лишь отличием, что вместо одного такта (SDRAM) за то же время передается пакет. Пакет ROW для второй транзакции пропущен, поскольку страницу оставили открытой. Транзакция чтения со стороны контроллера представляет собой петлю: он посылает пакеты команд, которые за некоторое время достигают целевой микросхемы и ею обрабатываются за время TCAC. Далее микросхема отвечает пакетом данных, которому для достижения контроллера также требуется некоторое время. Пакетам к и от дальних микросхем требуется для путешествий больше времени, чем ближним, и эта разница оказывается большей, чем длительность периода синхронизации. Для того, чтобы контроллер получал ответ на транзакцию чтения от любой микросхемы через одно и то же число тактов, у микросхем памяти устанавливают разную задержку данных относительно пакетов команд чтения. Группы соседних микросхем, у которых программируется одинаковая задержка, называют доменами синхронизации. В канале может быть несколько доменов синхронизации.

Страницы: 1, 2, 3, 4, 5, 6, 7, 8